Input/Output Controller IP

Welcome to the ultimate Input/Output Controller IP hub! Explore our vast directory of Input/Output Controller IP

All offers in

Input/Output Controller IP

Filter

Compare

14

Input/Output Controller IP

from

11

vendors

(1

-

10)

-

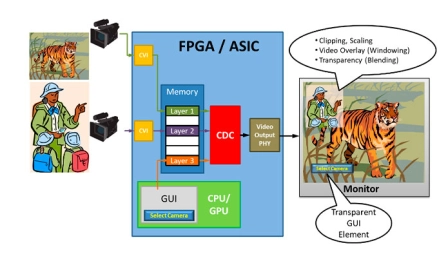

Customizable Display Controller IP

- CDC is a fully Customizable Display Controller IP supporting up to 16k resolutions (4096x4096 pixel) on a MIPI-DPI compliant parallel video output.

- Several features can be configured at synthesis time and programmed at run time.

- The display controller can be applied to e.g. FPGA systems with a resource optimized, application specific feature configuration or to ASIC projects applying a more generic feature set and thus more flexibility.

-

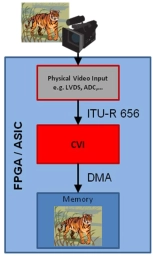

Customizable Video Input controller

- CVI is a fully Customizable Video Input controller IP core.

- The video input controller can be applied to e.g. FPGA systems with a resource optimized, application specific feature configuration or to ASIC projects applying a more generic feature set and thus more flexibility.

-

xSPI - PSRAM Master

- The xSPI/PSRAM master IP is easy to use, simple to work with, quick to operate, and reliable under all conditions. It supports the xSPI JESD~251 standard from a standard AXI3 or AXI4 slave interface.

- It also supports APMemory Octal/QSPI RAM, HyperRAM, HyperFlash, and features backwards compatibility support for Octal SPI, QSPI, DSPI, and SPI interfaces.

-

QSPI Master IP

- The QSPI master core is easy to use, simple to work with, quick to operate, and reliable under all conditions.

- It supports the majority of QSPI devices standard from a standard AXI4 slave interface. It also features support for Octal SPI, Dual SPI (DSPI), and SPI interface.

-

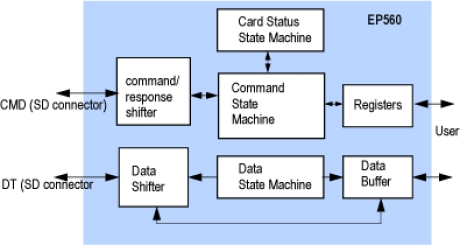

SDIO/SD Memory/MMC Slave Controller

- Compatible with SD/SDIO specification 2.0 with 1 and 4 bit data transfer.

- Provides SD interface to peripheral or memory device through a simple address/data interface.

- Support SD, SPI and optional MMC bus protocol.

- Support for both standard capacity and high capacity (SDHC) memory cards.

-

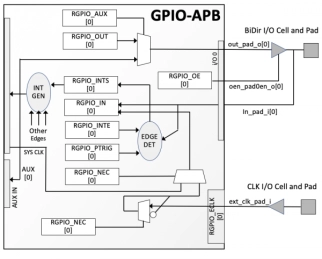

APB General Purpose IO (w/ interrupt)

- The APB GPIO is a configurable module allowing the use of up to 32 scalable I/O lines.

- If more than 32 I/Os are required, more than one GPIO module may be instantiated.

- Each line can be configured independently resulting in a very useful I/O application.

-

Intel 8255A Functional Equivalent Programmable Peripheral Interface

- The DB8255A Programmable Peripheral Interface core is a full function equivalent to the Intel 8255A / 82C55A and Intersil 82C55A devices.

- The DB8255A implements a general-purpose I/O interface connecting peripheral equipment to a microprocessor system bus.

- The core generates 24 programmable I/O lines which are individually programmed in 2 groups of 12 and used in 3 major modes of operation.

-

General-Purpose I/O Controller with APB Interface

- User selectable number of GPIO signals from 1 to 32

- All GPIO signals can be bi-directional (external bi-directional I/O cells are required in that case)

- All GPIO signals can be tri-stated or open-drain enabled (external tri-state or open-drain I/O cells are required in that case)

- GPIO signals programmed as inputs can cause an interrupt request to the CPU

-

APB4 General Purpose Input/Output Module

- Compliant with AMBA APB v2.0 Specification

- User-defined number of Bi-directional General Purpose IO

- Automatic synchronisation of General Inputs to Bus Clock

- Each General Output configurable as push-pull or open-drain

-

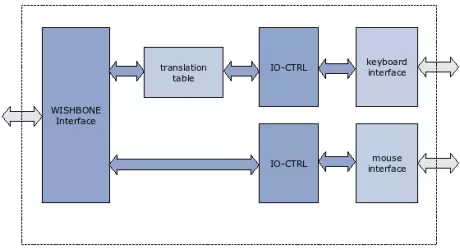

PS/2 Keyboard controller, fully configurable

- PS/2 core is used to communicate with either keyboard or mouse device

- PS/2 core can be configured to use single or dual connection signals within the same core

- AHB or WISHBONE SoC Interconnection Rev B compliant interface

- PS/2 can operate in pooling or interrupt mode